SISO (Serial In Serial Out):

- This shift register allows serial input and produces a serial output. As there is only one output, it delivers 1 bit at a time in a serial pattern. A 4-bit shift register using D flip-flops is illustrated below, with all flip flops connected in a serial manner and synchronized by the same clock signals.

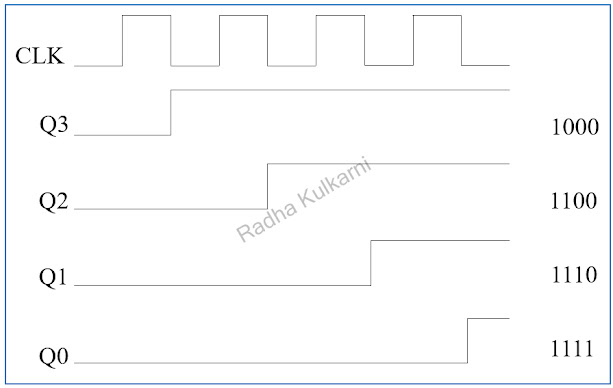

- Initially, all flip flops are in a reset condition (Q3=Q2=Q1=Q0=0). If the input data series is 1111, the first LSB bit (1) is considered as Din and is applied to the input of the first flip flop (D3). The output of the first flip flop is connected to the input of the second flip flop, and so on. The stored word in the register is updated on each falling edge of the clock signal, resulting in a sequential output.

- Before applying the clock signal, the output is initialized to Q3Q2Q1Q0=0000. Upon applying the clock signal, during the first falling edge of the clock, Flip-Flop 3 (FF3) is triggered, updating the stored word in the register to Q3Q2Q1Q0=1000.

- Subsequently, at the next negative edge of the clock, Flip-Flop 2 (FF2) is set, leading to a modification of the stored word to Q3 Q2 Q1 Q0=1100.

- Upon the occurrence of the third negative clock edge, Flip-Flop 1 (FF1) is activated, resulting in an output modification to Q3 Q2 Q1 Q0=1110.

- Finally, with the arrival of the fourth negative clock edge, the stored word in the register becomes Q3 Q2 Q1 Q0=1111.