- In this project, I have designed and implemented Vending Machine Controller using VHDL using Quartus Prime and Modelsim software.

- To explore the project you can git clone using this command: git clone Github

Table of Contents:

- INTRODUCTION

1.1 FSM (Finite State Machine) - RELATED WORK

- IMPLEMENTATION OF VENDING MACHINE

- DESIGN METHODOLOGY

- SIMULATION RESULTS

- CONCLUSION

- REFERENCES

1. INTRODUCTION

Vending Machine is an electronic machine used to dispense a product to a consumer after a prescribed amount of money has been put into the machine. Considering the current situation, the three most important things we need when we are outside are sanitizer, tissue paper, and paper soap for cleanliness and sanity purposes. So, we are designing a Vending Machine Controller using VHDL for sanitizer, tissue paper, and paper soap. This machine can be used at various places like railway stations, food stalls, etc.

The FPGA based Vending machines are reprogrammable, flexible, and more advantageous in terms of speed, response, and power consumption. FPGA based machines can be reprogrammed without the need to change the whole architecture when enhancing the model of the machine. Microcontrollers sequentially execute all operations whereas an FPGA is a field programmable gate array that will execute all your operations in a parallel fashion.

1.1 FSM (Finite State Machine) [2] [3]

In a Finite State Machine, the circuit’s output is defined in a different set of states i.e. each output is a state. A State Register to hold the state of the machine and a next state logic to decode the next state. An output register defines the output of the machine. In FSM based machines the hardware gets reduced as in this the whole algorithm can be explained in one process.

Two types of State machines are:

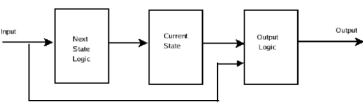

MEALY Machine: In this machine model, the output depends on the present state as well as on the input. The MEALY machine model is shown in figure 1.

MOORE Machine: In the Moore machine model the output only depends on the present state. The MOORE machine model is shown in figure 2.

2. RELATED WORK

Various researches have been carried out in order to design the Vending Machines. A few of them are discussed here as Ana Monga, Balwinder Singh [1] propose a vending machine for designing multi select machines using Finite State Machine Model with Auto-Billing Features. In this paper, the process of four states (user Selection, Waiting for money insertion, product delivery, and servicing) has been modeled using MEALY Machine Model. The proposed model is tested using Spartan 3 development board and its performance is compared with CMOS based machine. The various methods of designing VHDL based machines are discussed in [2], [3], and [4]. In the paper [5] Design and Implementation of an automatic Beverages Vending Machine and its performance evaluation using Xilinx ISE and Cadence, the design and implementation of an automatic beverages vending machine using FSM as this technique is compared with previous ones used in vending machine design and the whole design is verified using Xilinx ISE simulator 13.1 and the implemented using Virtex 5 XC5VLX50T FPGA board and its physical design has performed using Cadence Encounter and evaluated its optimized parameters.

3. IMPLEMENTATION OF VENDING MACHINE

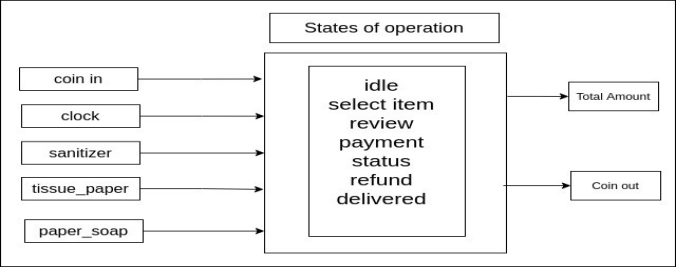

Vending machine for Sanitizer, tissue paper, and paper soap is designed using Quartus Prime Software. It can be deployed in the form of VHDL code, RTL view, and output waveform. The system will accept 3 inputs sanitizer, tissue paper, and paper soap, and will give the total cost. The complete cycle will run around 6 states idle, select item, review, payment status, refund, and delivered. If the amount is more than cost price change is returned and if the amount is less than the cost price complete amount is returned with no delivery.

4. DESIGN METHODOLOGY

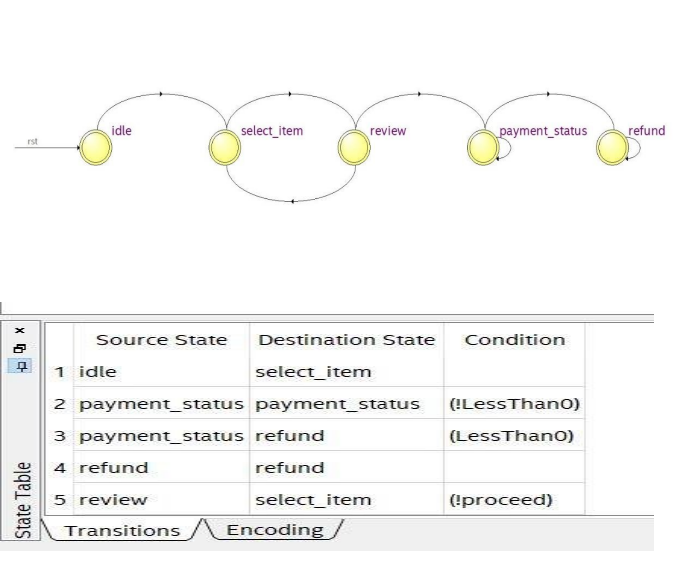

The code will accept three inputs and the system will run around 5 states idle, select_item, review, payment_status, and refund. Initially, it will be at an idle state and after each clock cycle, it will change its state. The next state will be select_item state where you can individually select from the given inputs and then it will go to review state where it will give you the total amount so you can check whether it is correct or not. If the total amount is correct it will go to payment_status state where you can enter the amount and it will then go in the refund based on comparing it with the total amount. If the cost entered is less than the total cost then it will refund the complete entered amount and will give no delivery similarly if the cost entered is more than the total cost it will refund the change and give the delivery.

Description of states

The selection of products and all the states is shown below:

when idle => p_s <= select_item ;

when select_item =>

temp := (10 *sanitizer + 5 *tissue_paper + 1 *paper_soap );

total <= temp ;

p_s <= review ;

when review =>

if (proceed =’1') then

p_s <= payment_status;

elsif(proceed = ‘0’ ) then

p_s <= select_item ; end if ;

when payment_status =>

if (temp <= coin_in) then

delivered <= ‘1’ ;

p_s <= refund ;

elsif(temp > coin_in ) then

delivered <= ‘0’ ;

coin_out <= coin_in ;

p_s <= payment_status;

end if ;

when refund => coin_out <= coin_in-temp;

Similarly, we can add other products also.

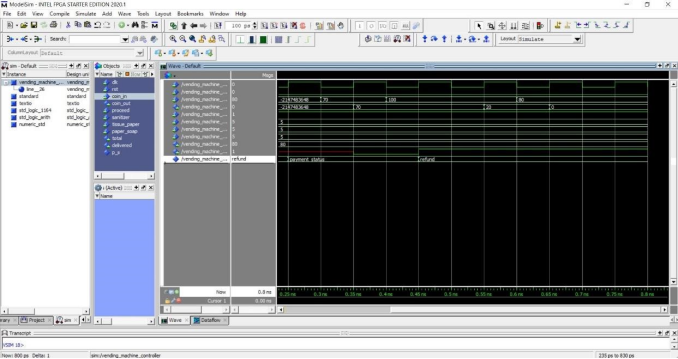

5. SIMULATION RESULTS

The Simulation is done using Modelsim software. Initially, the reset is set to 0 and the clock signal is given and then the state changes from idle to select_item state where I have selected 5 sanitizers, 5 tissue paper, and 5 paper soap. According to the pre-defined formula, the total amount must be 80 and we have received the same in the review state then we set to proceed to 1 and state changes to payment state where I have considered three different cases.

- In the first state, I have set the coin into 70 which is less than the total amount so according to the code it must return the whole amount i.e. 70 in the refund section and the delivered signal must be 0 and we have successfully got the same results.

- In the second state, the coin in input is set to 100 which is more than the total amount hence it must return 20 in the refund section and the delivered signal must become 1 and we have successfully got the results of the 2nd case correctly

- Now, in the third state, I have considered an idle state where we have entered the correct coin in the amount which is 80, and hence it should return 0 in the refund section and the delivered signal must be 1, here also we have successfully got the correct results.

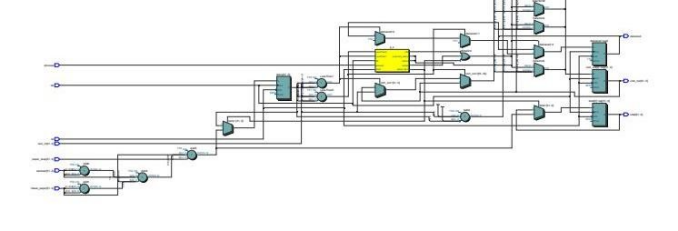

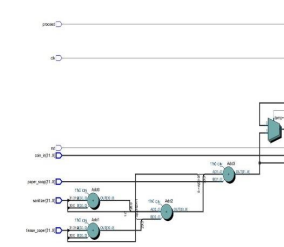

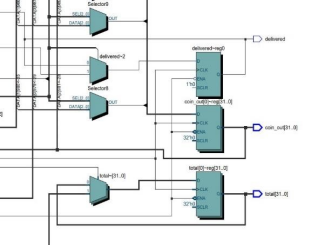

The below figure shows the complete RTL view:

I have divided the RTL view into two sections in the below figure as input and output part of the RTL view.

6. CONCLUSION

The above system can be implemented using any FPGA Development Board where you can select the items using on-off buttons and similarly display the amount and its status using LCD or OLED. State machine based vending Systems increases productivity reduces system development cost and accelerates the time to market. We can easily increase the number of inputs and also add different features to the system.

7. REFERENCES

- Ana Monga, Balwinder Singh “Finite State Machine based Vending Machine Controller with Auto-Billing Features” International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, №2, April 2012.

- Xilinx Inc., Spartan 3 Datasheet: http://www.xilinx.com.

- Bhaskar “VHDL primer” Second Edition,

- C. J Clement Singh, K Senthil Kumar, Jayanto Gope, Suman Basu & Subir Kumar Sarkar (2007) “Single Electron Device based Automatic Tea Vending Machine*” proceedings of International Conference on Information and Communication Technology in Electrical Sciences (ICTES 2007),* pp 891–896.

- V.V.S.Vijay Krishna, A. Monisha, Sk.Sadulla, J. Prathiba “Design and Implementation of an automatic Beverages Vending Machine and its performance evaluation using Xilinx ISE and Cadence” IEEE — 31661