Clock skew refers to the varying arrival times of the clock signal in synchronous circuits, while slack is the difference between the desired and actual arrival times of a signal.

Skew:

1) Clock skew is a phenomenon in synchronous circuits in which the clock signal (sent from the clock circuit or source) arrives at different components at different times. Similarly, slack is the difference between the desired arrival time and the actual arrival time for a signal.

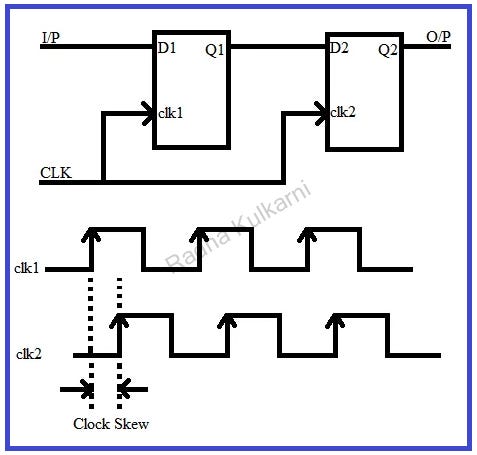

2) To illustrate clock skews let’s consider an example:

Here, we have two flip flops connected in series and clock signal is applied to the input of both flip flops. Output of 1st flip flop is connected to the input of another flip flop. clk1 serves as the clock input for the first flip flop and clk2 as the clock input for the second. Consider, clock input clk is applied to both clock inputs clk1 and clk2. Here, clk will arrive at both clock inputs are different timings. Consider, clock source clk reaches clk1 at time t and it reaches clk2 at time t+n. Hence, here skew is the difference between arrival of both clk timings which is (t+n)-t which is n. Here n is the clock skew.

3) A skew in a design occurs when one flip flop is situated far from the clock source compared to another nearby flip flop.

4) Local skew: Local skew refers to the difference in arrival times of the clock signal for directly connected flip flops.

5) Global skew: Global skew refers to the difference in arrival times of the clock signal for non-connected flip flops.

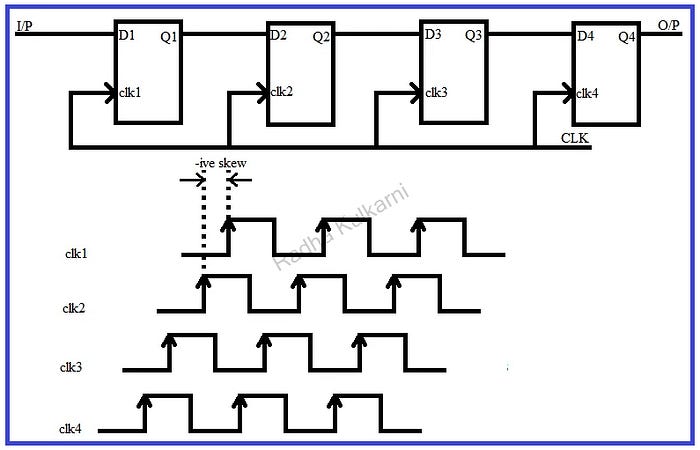

6) Skews can be positive and negative depending on the direction of clock and data:

- Positive Skew: Consider below diagram for understanding positive skew. Here both clock and data are in the same direction hence it results in a positive skew.It leads to hold time violation and improves the set up time violation.

- Negative skew: Similarly from the below diagram we can see that the direction of clock and dat ais oppostite and hence it will result in negative skew. It leads to setup time violations and improves the hold time violation.

Slack:

Slack is the difference between the desired arrival time and the actual arrival time for a signal. To gain proper understanding of slack in STA, consider the diagram below:

Here, we have two flip flops connected in series and clock signal is applied to the input of both flip flops. and output of 1st flip flop is connected to the input of another flip flop. clk1 is the clock input for 1st flip flop and clk2 is the clock input for 2nd flip flop. Input clock CLK is applied to both flip flops.

Setup and hold slack refers to the difference between desired arrival time and actual arrival time.

Required Time: The required time is the duration within which data must arrive at some internal node of the design.

Arrival Time: The arrival time is the time at which data arrives at the internal node, encompassing all net and logic delays between the reference input point and the destination node.

Hence, Setup Slack = Required time-arrival time

and Hold Slack = Arrival time-Required time

Slack time determines, if the design is working at the desired frequency.

Positive slack: A positive slack means that the timing requirements are being met and there is still room for improvement.

Negative slack: A negative slack means that the design has not achieved the specified timing at the required frequency.

Zero slack: A zero slack means that the design is critically working at the desired frequency.

It is essential to maintain positive slack at all times, and negative slack indicates a timing violation.

In conclusion, Clock skew and slack management are integral parts of VLSI design, ensuring the proper functioning and timing integrity of digital circuits. Clock skew refers to the variations in arrival times of the clock signal at different components within a circuits. It can lead to synchronization issues between flip flops and impact overall system performance. Understanding and controlling local and global skew are essential for designing synchronous circuits that operate reliably and efficiently.

Slack, on the other hand, represents the timing difference between desired and actual signal arrival times. Positive slack indicates that timing requirements are being met with room for improvement, while negative slack signifies timing violations that must be addressed. Maintaining positive slack is crucial for ensuring that circuit function correctly within specified timing constraints and avoid potential timing-related failures. Effective strategies such as careful clock distribution planning, minimizing signal propagation delays, and employing robust timing analysis tools are fundamental in managing clock skew and slack, ultimately contributing to the successful implementation of VLSI designs in practical applications.

No comments:

Post a Comment