Welcome to the world of digital design! In this blog post, we’ll dive into Verilog code examples for essential logic gates used in digital circuits. Understanding how to implement these gates is foundational for building complex digital systems.

For a detailed insight into how these logic gates operate, including their truth tables, click on the link provided below:

Logic Gates

Below, you’ll find Verilog code implementations for various logic gates using two different methods:

1. Behavioral Modeling: Describes the logic behavior using `always @(*)` blocks.

2. Dataflow Modeling: Describes the logic using continuous assignments (`assign`).

1. AND Gate

Behavioral Modeling:

module AND_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = a & b;

end

endmoduleDataflow Modeling:

module AND_Gate(input wire a, input wire b, output wire y);

assign y = a & b;

endmodule2. OR Gate

Behavioral Modeling:

module OR_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = a | b;

end

endmoduleDataflow Modeling:

module OR_Gate(input wire a, input wire b, output wire y);

assign y = a | b;

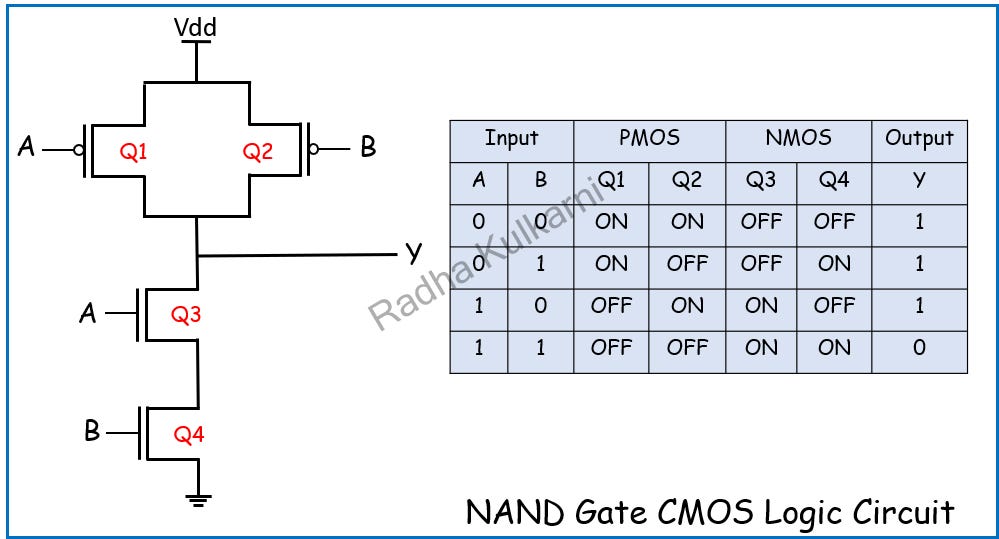

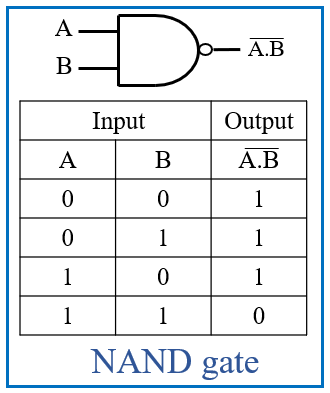

endmodule3. NAND Gate

Behavioral Modeling:

module NAND_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = ~(a & b);

end

endmoduleDataflow Modeling:

module NAND_Gate(input wire a, input wire b, output wire y);

assign y = ~(a & b);

endmodule4. NOR Gate

Behavioral Modeling:

module NOR_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = ~(a | b);

end

endmoduleDataflow Modeling:

module NOR_Gate(input wire a, input wire b, output wire y);

assign y = ~(a | b);

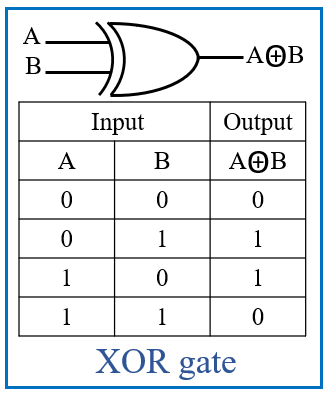

endmodule5. XOR Gate

Behavioral Modeling:

module XOR_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = a ^ b;

end

endmoduleDataflow Modeling:

module XOR_Gate(input wire a, input wire b, output wire y);

assign y = a ^ b;

endmodule6. XNOR Gate

Behavioral Modeling:

module XNOR_Gate(input wire a, input wire b, output reg y);

always @(*) begin

y = ~(a ^ b);

end

endmoduleDataflow Modeling:

module XNOR_Gate(input wire a, input wire b, output wire y);

assign y = ~(a ^ b);

endmoduleConclusion

These Verilog code snippets demonstrate two ways of implementing logic gates:

- Behavioral Modeling is more abstract and suitable for complex logic, using `always` blocks to describe how the logic should behave.

- Dataflow Modeling is closer to the gate-level, where continuous assignments (`assign`) directly describe how the inputs connect to the outputs.

Experiment with both methods to understand their behavior and use them as building blocks for creating sophisticated digital designs.