Timing closure in VLSI design refers to the process of ensuring that a digital circuit meets all its timing requirements, such as setup time, hold time, clock skew, and signal propagation delays, across all possible operating conditions and process variations. It is a critical step in the design flow that verifies the circuit can function correctly at the desired clock speed without timing violations.

Why Timing Closure is Important:

- Ensuring correct circuit operation without timing violations is essential for functionality. Failure to achieve timing closure can lead to performance issues and errors.

- Meeting timing requirements allows the circuit to run at its maximum clock speed, optimizing performance, especially in high-speed applications. Achieving timing closure guarantees reliability across varying conditions and is crucial for both consumer electronics and critical applications.

- Proper timing closure also enhances power efficiency by minimizing unnecessary power consumption. Additionally, it facilitates manufacturing by reducing the risk of non-functional chips, improving yield, and lowering costs associated with re-spins and debugging.

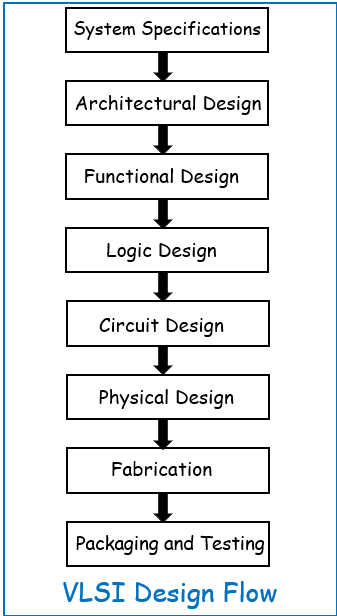

Process of Timing Closure:

- Achieving timing closure in VLSI design involves several critical steps. Static Timing Analysis (STA) is a key tool used for this purpose, analyzing the timing paths in the circuit without requiring dynamic simulation to ensure that all paths meet their timing requirements.

- The process often involves iterative optimization, where adjustments are made to the design to fix timing violations. This can include resizing gates, adjusting placement and routing, and optimizing the clock tree.

- Clock Tree Synthesis (CTS) is another crucial step, ensuring that the clock distribution network meets timing requirements, reducing skew and jitter.

- Additionally, physical design adjustments, such as changes in placement, routing, and layout, are made to minimize delays and improve timing performance. Finally, sign-off verification is conducted to ensure that the design meets all timing constraints before tape-out.

In summary, timing closure is a vital aspect of VLSI design, ensuring that the circuit performs correctly and reliably at the desired speed, optimizing both performance and power efficiency.