Welcome back to the Analog Electronics series!

In this chapter, we dive into one of the most fundamental concepts in the world of electricity — electric charge — the invisible quantity behind every electric and magnetic phenomenon we study.

We’ll also explore Coulomb’s Law and the idea of permittivity, which together help us understand how materials behave when exposed to an electric field — the foundation of capacitors, dielectrics, and even semiconductor behavior.

Let’s get started 👇

⚡ Electric Charge

Electric charge is a fundamental property of matter that causes it to experience a force of attraction or repulsion when placed in an electric or magnetic field. It is one of the most basic and conserved quantities in nature, similar to mass.

Every atom consists of electrons, protons, and neutrons:

- Mass of electron (me): 9.1 × 10⁻³¹ kg

- Mass of proton (mp): 1.6 × 10⁻²⁷ kg

- Mass of neutron (mn): 1.6 × 10⁻²⁷ kg

Electrons carry a negative charge, while protons carry an equal but positive charge. Neutrons are electrically neutral.

- Charge of electron = −1.6 × 10⁻¹⁹ C

- Charge of proton = +1.6 × 10⁻¹⁹ C

If a proton and an electron are placed 1 cm apart, they experience a force of attraction ≈ 2.3 × 10⁻²⁴ N.

The SI unit of electric charge is Coulomb ©, and the SI unit of force is Newton (N).

🔹 Quantization of Charge

Electric charge is quantized, meaning it exists only in discrete, indivisible packets — not in fractions. The smallest possible unit of charge is that of an electron or proton, represented by e = 1.6 × 10⁻¹⁹ C.

Any observable charge on a body is always an integer multiple of this basic unit:

Q=n×e

where n is an integer.

🔹 Conservation of Charge

Electric charge can neither be created nor destroyed in an isolated system. The total charge before and after any process — whether it’s rubbing, chemical reaction, or nuclear reaction — always remains constant.

Charge may transfer from one body to another, but the net charge of the entire system stays the same.

⚙️ Coulomb’s Law

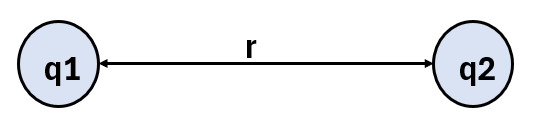

Coulomb’s Law defines the electrostatic force between two stationary point charges.

It states that:

“The electrostatic force between two charges is directly proportional to the product of their charges and inversely proportional to the square of the distance between them.”

Mathematically,

Where:

- F = electrostatic force between charges (in newtons, N)

- q₁, q₂ = magnitudes of the two charges (in coulombs, C)

- r = distance between the charges (in meters, m)

- k = Coulomb’s constant = 8.99 × 1⁰⁹ N·m²/C²

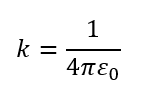

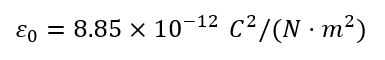

The constant k is related to the permittivity of free space (ε₀) by:

⚙️ Permittivity (ε)

Permittivity is a measure of how easily a material’s internal charges can shift to form tiny dipoles in response to an electric field — or simply, how easily an insulator can be polarized.

There are two types of permittivity:

1. Permittivity in Free Space (ε₀)

In a vacuum (free space), there are no atoms or molecules to polarize.

Even though there is nothing to shift, we still define ε₀ — the absolute permittivity of free space — because:

- It sets the baseline for all electric interactions.

- It defines how strong the electric force is in the absence of any material.

- Coulomb’s Law uses k = 1/(4πε₀) to calculate the force between two charges in empty space.

- It allows us to compare the behavior of materials with free space.

When we put a dielectric (like water or glass) between charges, we compare its permittivity ε to ε₀.

2. Permittivity of a Material (ε)

Permittivity of an insulator or dielectric refers to its ability to polarize when placed in an electric field.

When a dielectric (insulator) is placed in an electric field, charges cannot move freely as in conductors. However, electrons slightly shift opposite to the field, and protons shift slightly in the direction of the field.

This small separation of positive and negative charges forms tiny electric dipoles throughout the material.

The ability of a material to form these dipoles easily is called its permittivity (ε).

- High permittivity: Electrons and nuclei shift more easily → strong dipoles → the material reduces the electric field more.

- Low permittivity: Electrons and nuclei shift less → weak dipoles → the field is reduced less.

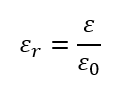

🔹 Relative Permittivity (εᵣ)

Relative permittivity (or dielectric constant) is the ratio of a material’s permittivity to that of free space:

It tells us how much the material reduces the electric field compared to vacuum.

🧭 Summary

- Charge is the basic property of matter responsible for all electric effects.

- Coulomb’s Law gives the force between two point charges.

- Permittivity (ε) represents how easily a material polarizes when placed in an electric field.

- Relative permittivity (εᵣ) compares the material’s polarization ability with that of free space.

✨ Closing Thoughts

Understanding electric charge and permittivity forms the foundation for analyzing how electric fields interact with materials — a key principle in designing capacitors, sensors, and semiconductor devices.

Stay tuned for Chapter 6, where we’ll explore the next concept in our Analog Electronics journey!