In the world of Very Large Scale Integration (VLSI), timing considerations are paramount. Two crucial concepts that engineers must grasp are setup time and hold time. These terms are fundamental to ensuring the correct operation of digital circuits, especially in synchronous systems. Let’s dive into what setup time and hold time mean, their significance, and how they impact VLSI design.

- Setup Time:

Setup time refers to the minimum amount of time a data signal must be stable and valid before the active edge of the clock signal arrives for proper data capture. In simpler terms, it is the time duration during which the input data must remain unchanged before the clock edge triggers the flip-flop to capture that data. If the data changes too close to the clock edge, it may lead to incorrect or unpredictable behavior in the flip-flop.

- Hold Time:

Hold time, on the other hand, is the minimum duration that the input data must remain stable and unchanged after the active clock edge transitions. This ensures that the flip-flop has enough time to store the correct data reliably. If the data changes too soon after the clock edge, it can cause hold time violations, potentially leading to metastability issues or incorrect data storage.

The concept of setup time and hold time mainly occurs while performing static timing analysis.

Let us consider an example of flip flop to understand setup time and hold time and why they are important in understanding metastability.

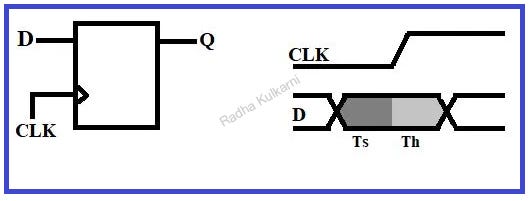

- Consider a D flip flop as shown in the above diagram. Here, input D is given to the flip flop, Q is the output, and clk is the clock cycle.

- In the waveform shown above, region one is the setup time region and region two is the hold time region.

- The setup time is the interval before the clock where the data must be held stable for the data to be latched correctly. Similarly, hold time is the interval after the clock where the data must be held stable.

- Here, the input D must remain stable and not change in the setup time before the clock occurs and it must also remain stable after the clock edge has occurred in region two i.e., during hold time.

- Aperture time can be defined as the total interval where input must remain stable which is setup time + hold time hence the flip flop must be stable during its aperture time.

- But why should it remain stable?

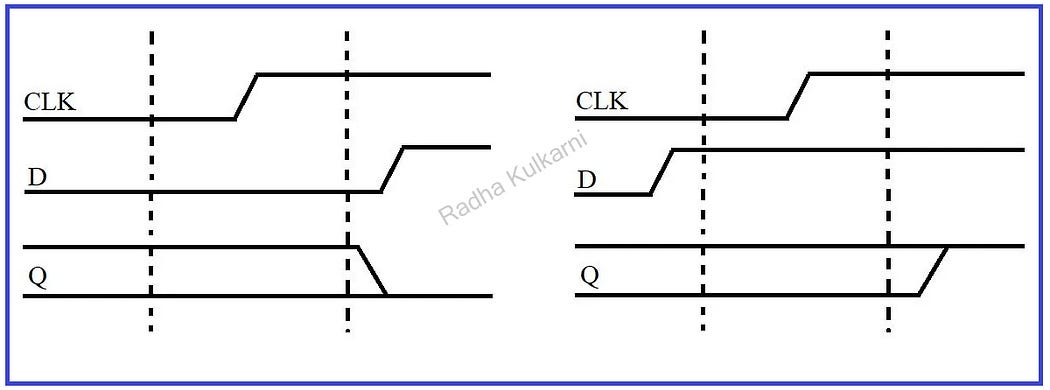

To understand this, we will consider 3 states as follow:

1] Consider that the input of the flip flop is stable for low value during aperture time. Then the output will take a low value.

2] Similarly, if the input of the flip flop is high in the aperture time, then the output will take a high value. This can be seen in the below diagram:

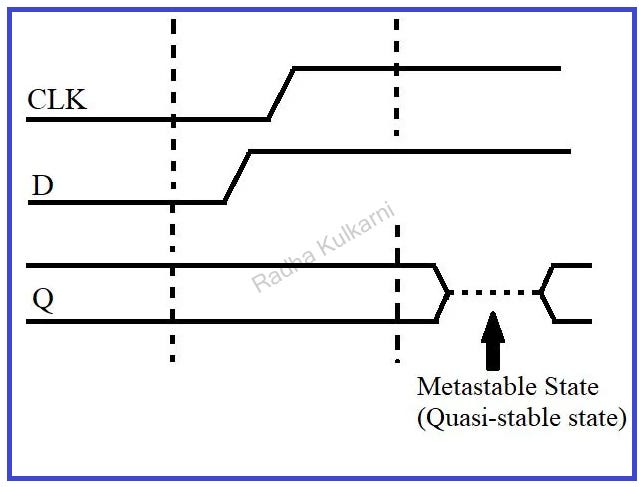

3] But if the input of the flip flop changes to a high or low value during the aperture time then the flip flop captures a value partway between low and high and this state is called the Metastable state or Quasi-stable state. This can be summarized in the below diagram.

The output will eventually take a high or a low value, but it will unlimited amount of time to settle or resolve to a good high or low value.

This process of flip-flop going into a metastable state and then getting into a high or a low state is called Metastability.

- Significance in VLSI Design:

Understanding setup time and hold time is crucial in VLSI design for several reasons:

- Timing Violations: Violating setup or hold time constraints can result in timing violations, leading to unreliable circuit operation and potential malfunctions.

- Metastability: Insufficient setup and hold times can cause metastability, where the flip-flop enters an unstable state, potentially resulting in incorrect output values.

- Clock Skew: Setup and hold times are affected by clock skew, which is the variation in arrival times of the clock signal at different parts of the circuit. Managing clock skew is essential to ensure proper setup and hold times are met.

- Performance and Reliability: Meeting setup and hold time requirements improves the overall performance and reliability of digital circuits, especially in high-speed designs.

Best Practices for Setup and Hold Time:

- Timing Analysis: Perform detailed timing analysis using EDA (Electronic Design Automation) tools to ensure that setup and hold time requirements are met under various operating conditions and corner cases.

- Clock Domain Crossing (CDC) Analysis: Pay special attention to signals crossing between different clock domains to prevent setup and hold time violations due to asynchronous interactions.

- Margin Consideration: Provide sufficient margin for setup and hold times to account for process variations, temperature changes, and voltage fluctuations, ensuring robust circuit operation across different conditions.

- Conclusion:

Setup time and hold time are critical concepts in VLSI design, ensuring the reliable and accurate operation of digital circuits. By understanding these timing parameters, engineers can design high-performance, robust, and error-free VLSI systems. Incorporating best practices, thorough timing analysis, and careful consideration of clock domains are key to meeting setup and hold time requirements effectively.