Hard disk drives (HDDs) are the backbone of data storage, enabling us to store vast amounts of information reliably. Ever wondered how HDDs achieve precise data storage and retrieval? Behind the scenes, a specialized integrated circuit (IC) plays a crucial role in ensuring precision and efficiency. This blog will break down how this IC functions within an HDD, by breaking down key components and their functions.

What are Hard Disk Drives?

A hard disk drive (HDD) is a data storage device used in computers, servers, and external storage systems. It stores digital data using magnetic storage on rapidly spinning disks (platters). These platters are coated with a magnetic material, and data is written or read using an actuator arm with a read/write head.

Where Are HDDs Used?

Hard disk drives are found in:

✔ Personal computers & laptops — For storing the operating system, files, and applications.

✔ Data centers & cloud storage — Large-capacity HDDs are used to store massive amounts of data.

✔ Surveillance systems — Security cameras record and store video footage on HDDs.

✔ Gaming consoles & external drives — HDDs provide additional storage for games and media.

The Role of Specialized ICs in HDDs

The accuracy and speed of reading and writing data in an HDD are managed by a specialized integrated circuit (IC). This IC processes signals, controls data flow, and ensures the magnetic head precisely reads and writes data on the disk surface.

Understanding the Read, Write, and Servo Operations in HDDs

1. Read Process — How Data is Retrieved

Reading data from an HDD involves extracting weak magnetic signals from the spinning disk and converting them into digital information. This process happens through the following stages:

🔹 VGA (Variable Gain Amplifier) — The signal received from the read head is very weak, so the VGA amplifies it to a readable level.

🔹 Low Pass Filter — Filters out high-frequency noise from the signal.

🔹 Summation & PLL (Phase-Locked Loop) — The summation block adjusts the signal before conversion. The PLL is crucial here as it extracts timing information and synchronizes data recovery with the disk’s rotation speed. Without a PLL, reading data accurately would be difficult.

🔹 6-bit ADC (Analog-to-Digital Converter) — Converts the analog signal into digital form.

🔹 FIR (Finite Impulse Response) Filter — Removes unwanted noise and optimizes the signal for detection.

🔹 Sequence Detector — Identifies the data pattern stored on the disk. Many modern HDDs use Viterbi detectors instead of simple sequence detection for better accuracy.

🔹 RLL Decoder & Randomizer — Converts the detected pattern into usable data and removes randomness added during the writing process.

🔹 To Disk Controller — The final digital data is sent to the disk controller, which communicates with the computer.

The Read/Write IC is designed to handle these steps seamlessly, ensuring that even tiny fluctuations in the magnetic signal do not result in data loss or corruption.

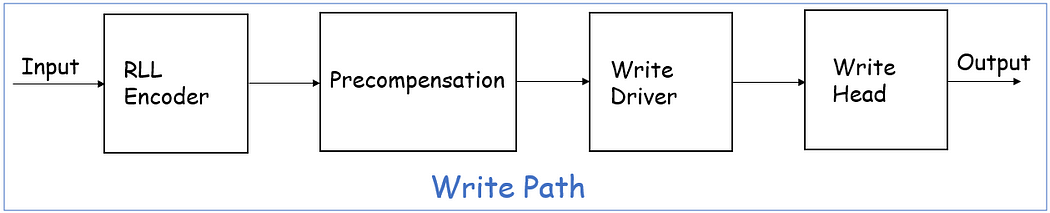

2. Write Process — Storing Data on the Disk

Writing data onto an HDD platter involves precise encoding and precompensation to ensure accuracy. When data is written to a hard disk, it must be converted into a format that the magnetic disk can store. This process involves several steps:

🔸 RLL (Run-Length Limited) Encoding — Converts data into a format suitable for magnetic storage. Incoming digital data is encoded to ensure efficient use of the magnetic surface and improve data recovery reliability.

🔸 Write Precompensation — Write Precompensation slightly shifts the timing of magnetic transitions during writing to counter the interference caused by closely packed magnetic domains, improving data integrity in high-density HDDs.

🔸 Write Driver — Provides the necessary current to induce controlled magnetic transitions on the disk surface. This component amplifies the encoded data signals before sending them to the write head.

🔸 Write Head — Writes the data onto the spinning disk by flipping magnetic domains. The write head generates a changing magnetic field that alters the orientation of particles on the spinning disk surface, storing the data permanently.

The specialized IC ensures that each of these steps happens precisely, minimizing errors and optimizing data placement for fast retrieval.

3. Servo System — Positioning the Read/Write Head

To ensure accurate reading and writing, HDDs use a servo system that continuously adjusts the read/write head’s position over the correct track. The Servo IC plays a vital role in this by continuously monitoring the head’s position using:

- High Pass Filter & Low Pass Filter — These filters help in extracting position-related signals from noise.

- Demodulator — Converts position signals into a format usable by the controller.

- Peak Detector — Identifies signal peaks to accurately determine track alignment.

- Bit Detector — Processes the final position data, allowing adjustments in head movement.

This servo feedback loop ensures that the read/write head stays perfectly aligned, allowing for accurate data access.

While HDDs appear simple externally, their functionality depends on intricate electronics and advanced signal processing techniques. The specialized ICs inside an HDD play a crucial role in signal amplification, data recovery, error correction, and precise head positioning. Without these advanced circuits, modern hard drives wouldn’t be able to store or retrieve data reliably.

Understanding how these ICs manage read, write, and servo operations gives us a deeper appreciation of the technology that powers our digital world. Whether it’s storing documents, playing high-definition videos, or running software applications, the hard drive’s internal electronics ensure seamless performance behind the scenes.

Do you find storage technology fascinating? Share your thoughts in the comments below!