PIPO (Parallel In Parallel Out):

- A Parallel-In-Parallel-Out (PIPO) shift register is a type of digital shift register that allows parallel input data to be loaded into the register and simultaneously produces parallel output data. Unlike Serial-In-Serial-Out (SISO) or Parallel-In-Serial-Out (PISO) shift registers, a PIPO shift register enables parallel transfer of data both at the input and output.

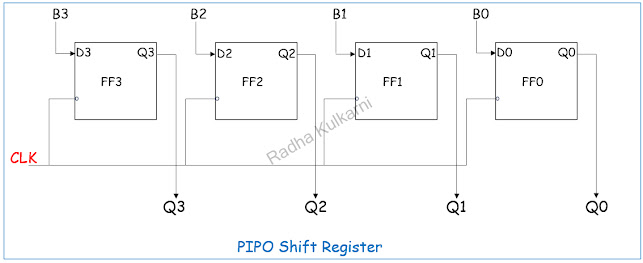

Here’s a brief overview of how a 4-bit PIPO shift register works:

- Initially, all flip-flops in the PIPO shift register are set to a reset state (Q3 Q2 Q1 Q0 = 0000). Apply the parallel input data (D3 D2 D1 D0) to the respective inputs of each flip-flop. Each flip-flop stores one bit of the parallel input data. On the rising or falling edge of the clock signal (depending on the design), the parallel input data is latched into the flip-flops simultaneously.

- The data in all flip-flops are available simultaneously at the parallel outputs (Q3 Q2 Q1 Q0). The PIPO shift register retains the parallel data until new parallel data is provided and clocked in.

- A key characteristic of the PIPO shift register is its ability to perform parallel transfers at both the input and output stages. This makes it suitable for applications where parallel data needs to be maintained and processed concurrently.

No comments:

Post a Comment