The Field Effect Transistor (FET) is a semiconductor device that uses an electric field to control the flow of current in the semiconductor. It has 3 terminals: source, gate, and drain. Here, the current flows between drain and source terminal and it can be controlled by applying a voltage between gate and source.

This voltage between gate and source (Vgs) generates an electric field. By controlling this electric field or voltage we can control the flow of current in the device. Hence it is called a voltage-controlled device. Unlike BJT, FET is a unipolar device i.e., it is dependent on either holes or electrons. FETs can be used in amplifiers, analog switches, integrated circuits, oscillators, etc. It can also be used as a buffer amplifier as it has a very high input impedance. They are smaller in size compared to BJTs and hence used in ICs. They also have low power consumption compared to BJTs.

FETs can be divided into 2 types:

1] JFET — Junction Field Effect Transistor

2] IG-FET — Insulated Gate Field Effect Transistor OR

MOSFET — Metal Oxide Semiconductor Field Effect Transistor

As we know that the current flows between drain and source and the path through which it flows is called a channel. Based on the channel material FET can further be divided into 2 types:

1] n-channel

2] p-channel

JFET:

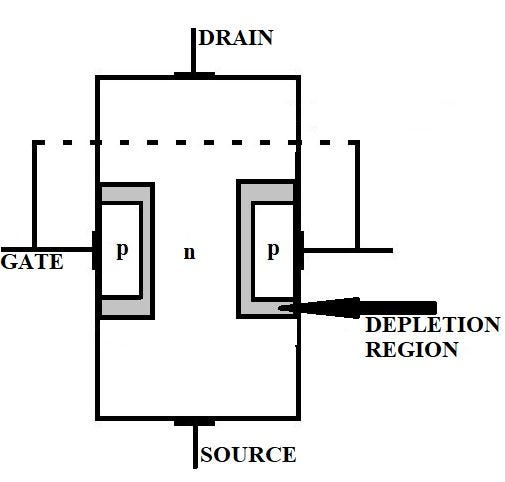

In the case of n channel JFET, the channel is made up of n-type material and similarly, in p channel JFET, the channel is made up of p-type material. The below figure shows the basic structure of the n channel JFET in which the channel is made up of n-type material and has 2 p-type materials.

Here, using ohmic contacts drain terminal is connected to the top of the n channel, and the source is connected to the bottom of the n channel, and both p-type regions are connected together and connected to the gate terminal. Here, we have 2 p-type regions which result in 2 P-N junctions and the formation of depletion regions.

Working:

When voltage is applied between drain and source terminal current starts from between drain and source terminal and this current can be controlled by applying a voltage between gate and source.

Below figure shows the Circuit diagram of n channel JFET:

Connections are as follows:

1] Gate and source terminals are connected together and the voltage between them is called Vgs.

2] Source terminal is connected to the ground.

3] Drain and Source terminals are connected together and the voltage between them is called Vds.

For n channel JFET, the voltage between source and drain is positive.

5]Voltage Vdd is applied between the source and drain.

When we apply Vdd voltage electrons start flowing from source to drain and the conventional current flows from drain to source.

Consider, Vgs is zero and Vds is positive for n channel JFET. As Vds is positive both PN junctions will be reverse biased and will result in an increase in the depletion region.

From the above figure, we can observe that the depletion region is wider at the top of the p-type region and narrow at the bottom. This is because the n channel acts as a resistor and assume that there is uniform resistance throughout the channel. This n channel can be observed as a series of resistors distributed between drain and source as shown in the below figure:

Now, when we apply drain current(Id) there will be a voltage drop across each resistor. Consider the voltage at the top as 2V and as we move towards the source there will be a voltage drop across each resistor. Hence, the upper region of p-type material is more reverse biased than the lower region. Here, due to the increasing depletion region, only a small amount of reverse saturation current will flow through this PN junction.

As the PN junctions are reverse biased the input impedance of the JFET is very high. As we increase the voltage Vds between the drain and source the current through the channel will also increase. The below figure shows the graph of Id vs Vds which is also known as the Output characteristics of JFET.

For low Vds voltage, the graph is almost a straight line as we increase the Vds voltage the depletion region will become wider and wider as shown in the below figure. Due to this reduced channel width, the resistance of the channel will increase and reduce Id current. As we further increase the Vds voltage the two depletion regions will touch each other as shown in the below figure.

This condition is known as the Pinch-off condition and the voltage at which this occurs is known as pinch-off voltage. Hence when Vds is greater than or equal to Vp(pinch off voltage ) pinch off condition will occur. Once this pinch-off condition occurs Id current will stop flowing. But practically Id current will not be 0 but will be maximum.

Hence,

Id= Idss when

Vgs = 0 and Vds≥Vp.

Therefore when JFET is in the pinch-off condition it will show constant Id current.

Here we are considering that the voltage between gate and source Vgs is 0 but we know that Vgs voltage can change the Id current. So to see the change in output characteristics we will make the Vgs voltage more negative with respect to zero voltage. Consider, the Vgs voltage as -1V. Due to negative voltage the depletion region will be created across the PN junction and as we increase the Vds voltage depletion region will go on increasing but the pinch-off condition will occur at lower values of Vds Because as the Vgs voltage is negative the PN junction is already reverse biased. The below figure shows the output characteristics of JFET with different values of Vgs voltage.

Here, you can see that the pinch-off condition will occur at lower values of Vds voltage as we reduce the Vgs voltage. So when you reduce the value of Vgs voltage from -1V to -4V and further reduce it equal to -Vp the current will reduce to 0 and this region of operation is known as the cut-off region.

In this way, the JFET can be operated in three different regions: the ohmic region saturation region, and the cut-off region. In the ohmic region, the JFET will work as a variable resistor. Similarly in the saturation region when Vds is greater than Vp the drain current Id will be constant and as we know in the cut-off region the Id current will be 0.

In this way, the JFET will function with respect to changes in different voltages.