When working with Verilog, two constructs that can greatly enhance the flexibility and reusability of your code are parameter and generate. These constructs allow you to create more modular and adaptable designs. In this blog, we’ll delve into how these features work and how you can use them effectively in your Verilog code.

Understanding parameter in Verilog

The parameter keyword in Verilog is used to define constants that can be used throughout your module. Parameters allow you to make your design more flexible by allowing you to modify the behavior of your module through parameterization rather than hardcoding values.

- Why Use Parameters?

- Flexibility: Parameters allow you to easily change values without modifying the core module code.

- Reusability: You can create more generic and reusable modules by adjusting parameters.

- Readability: Using parameters can make your code more readable and maintainable.

- How to Define and Use Parameters

To define a parameter, use the following syntax:

module my_module #(parameter WIDTH = 8, parameter DEPTH = 16) (

input [WIDTH-1:0] data_in,

output [WIDTH-1:0] data_out

);

// Module implementation

endmoduleIn this example, WIDTH and DEPTH are parameters with default values of 8 and 16, respectively. You can override these default values when you instantiate the module:

my_module #(.WIDTH(16), .DEPTH(32)) instance1 (

.data_in(data_in_16),

.data_out(data_out_16)

);Example: Parameterized Adder

Objective: Create a simple parameterized adder module that can be configured for different bit-widths.

Code:

module adder #(parameter WIDTH = 8) (

input [WIDTH-1:0] a,

input [WIDTH-1:0] b,

output [WIDTH-1:0] sum,

output carry_out

);

assign {carry_out, sum} = a + b;

endmoduleExplanation:

- parameter WIDTH = 8: This parameter allows you to specify the width of the adder. The default value is 8 bits.

- input [WIDTH-1:0] a, b: Inputs

aandbare vectors with a width specified by theWIDTHparameter. - output [WIDTH-1:0] sum: The output

sumhas the same width as the inputs. - assign {carry_out, sum} = a + b: Adds

aandb, assigning thesumandcarry-out.

Instantiation:

adder #(.WIDTH(4)) adder_4bit (

.a(4'b1010),

.b(4'b0101),

.sum(sum_4bit),

.carry_out(carry_out_4bit)

);

adder #(.WIDTH(16)) adder_16bit (

.a(16'h1234),

.b(16'h5678),

.sum(sum_16bit),

.carry_out(carry_out_16bit)

);This example creates two instances of the adder module: one with a 4-bit width and another with a 16-bit width.

Exploring generate in Verilog

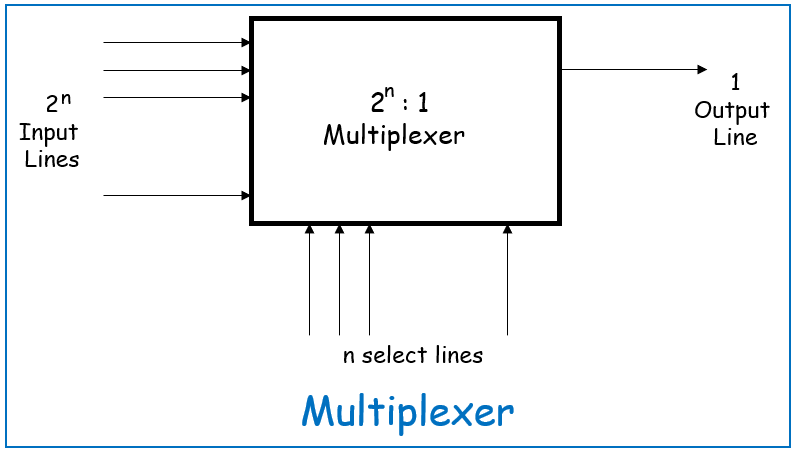

The generate construct is used to create multiple instances of a module or logic based on a parameter or a condition. This can be particularly useful for generating repetitive structures such as arrays of registers or counters.

- Why Use Generate?

- Code Reduction: Helps reduce repetitive code by allowing you to generate multiple instances or structures with a single block of code.

- Conditional Instantiation: Allows you to instantiate modules or logic conditionally based on parameters.

- Basic Syntax of Generate

The generate construct is used in conjunction with genvar and for loops to create multiple instances:

module generate_example #(parameter N = 4) (

input [N-1:0] in,

output [N-1:0] out

);

genvar i;

generate

for (i = 0; i < N; i = i + 1) begin : gen_block

assign out[i] = in[i]; // Example: copying input to output

end

endgenerate

endmoduleIn this example, the generate block creates N instances of the assign statement. The genvar keyword is used to declare a variable for use in the generate block.

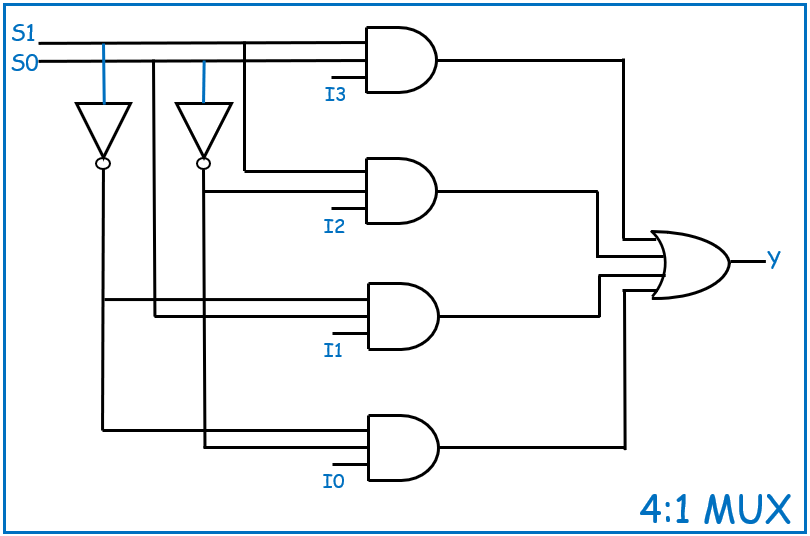

Example: 2-to-1 Multiplexer Array

Objective: Use generate to create multiple instances of a 2-to-1 multiplexer.

Code:

module mux2to1 #(parameter WIDTH = 8) (

input [WIDTH-1:0] a,

input [WIDTH-1:0] b,

input sel,

output [WIDTH-1:0] y

);

assign y = sel ? b : a;

endmodule

module top_module #(parameter NUM_MUX = 4) (

input [NUM_MUX*8-1:0] data_in,

input [NUM_MUX-1:0] sel,

output [NUM_MUX*8-1:0] mux_out

);

genvar i;

generate

for (i = 0; i < NUM_MUX; i = i + 1) begin : mux_gen

mux2to1 #(.WIDTH(8)) mux_instance (

.a(data_in[i*8 +: 8]),

.b(data_in[(i+1)*8-1 -: 8]),

.sel(sel[i]),

.y(mux_out[i*8 +: 8])

);

end

endgenerate

endmoduleExplanation:

- mux2to1 Module: A parameterized 2-to-1 multiplexer with a configurable data width.

- top_module: Uses a generate block to create multiple instances of the mux2to1 module.

- genvar i: A generate variable used to iterate through the for loop.

for (i = 0; i < NUM_MUX; i = i + 1): Loop generates NUM_MUX instances of mux2to1. - data_in[i*8 +: 8]: Extracts an 8-bit segment from data_in for the a input.

- mux_out[i*8 +: 8]: Collects the output from each multiplexer instance.

Instantiation:

top_module #(.NUM_MUX(4)) top_instance (

.data_in({32'hA5A5A5A5, 32'h5A5A5A5A, 32'hFFFF0000, 32'h0000FFFF}),

.sel(4'b1010),

.mux_out(mux_out)

);In this example, top_instance creates a 4-way multiplexer where each instance of mux2to1 is configured to select between pairs of 8-bit inputs.

Conclusion

The parameter and generate constructs in Verilog provide powerful tools for creating flexible, reusable, and efficient designs. Parameters enable you to adjust module behavior and design size without modifying the core module, while the generate construct helps in managing repetitive structures and conditional instantiation.

By mastering these constructs, you can enhance the adaptability and maintainability of your Verilog code, making it more robust and scalable for complex designs.