up_down_counter.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity up_down_counter is

Port ( clk: in std_logic;

reset: in std_logic;

enable: in std_logic;

counter: out std_logic_vector(3 downto 0)

);

end up_down_counter;

architecture Behavioral of up_down_counter is

signal count: std_logic_vector(3 downto 0);

begin

process(clk)

begin

if(rising_edge(clk)) then

if(reset=’1') then

count <= x”0";

elsif (enable = ‘0’)then

count <= count + x”1";

else

count <= count — x”1";

end if;

end if;

end process;

counter <= count;

end Behavioral;

tb_up_down_counter.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity tb_up_down_counters is

end tb_up_down_counters;

architecture Behavioral of tb_up_down_counters is

component up_down_counter

Port ( clk: in std_logic;

reset: in std_logic;

enable: in std_logic;

counter: out std_logic_vector(3 downto 0)

);

end component;

signal reset,clk, enable: std_logic;

signal counter:std_logic_vector(3 downto 0);

begin

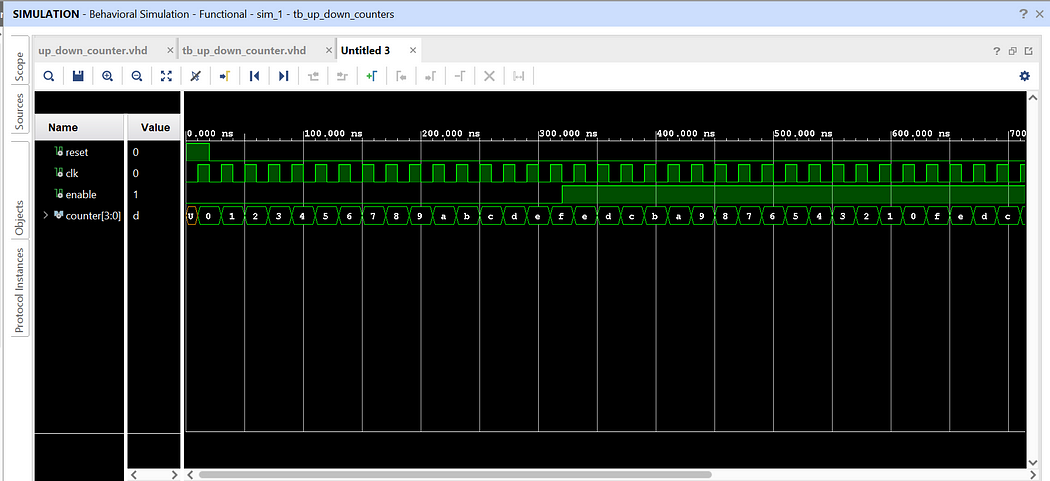

dut: up_down_counter port map (clk => clk, reset=>reset, enable=>enable, counter => counter);

— Clock process definitions

clock_process :process

begin

clk <= ‘0’;

wait for 10 ns;

clk <= ‘1’;

wait for 10 ns;

end process;

— Stimulus process

stim_proc: process

begin

— hold reset state for 100 ns.

reset <= ‘1’;

enable<=’0';

wait for 20 ns;

reset <= ‘0’;

wait for 300ns;

enable<=’1';

wait;

end process;

end Behavioral;

No comments:

Post a Comment