- CMOS technology, abbreviated for Complementary Metal-Oxide-Semiconductor, stands as a cornerstone in modern digital design, serving as the backbone for numerous electronic devices. This blog aims to explore the intricacies of CMOS technology, encompassing its fundamental principles, transistor structure, advantages, fabrication process, applications in VLSI design, and future prospects.

- At the core of CMOS technology lies the utilization of both NMOS (N-channel Metal-Oxide-Semiconductor) and PMOS (P-channel Metal-Oxide-Semiconductor) transistors. Diverging from the traditional TTL (Transistor-Transistor Logic), CMOS distinguishes itself with its exceptional attributes, including low power consumption and remarkable noise immunity, rendering it a preferred choice for contemporary digital circuits.

- By employing complementary pairs of p-type and n-type MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors), CMOS technology enables symmetrical and efficient logic functions. This technology finds extensive use in crafting integrated circuit (IC) chips, ranging from microprocessors and microcontrollers to memory chips (including CMOS BIOS) and various digital logic circuits.

- Structure and operation:

- In CMOS technology, the structure involves connecting the gate terminals of both NMOS and PMOS transistors together. The VDD (power supply voltage) is connected to the source of the PMOS transistor, while GND (ground) is connected to the source of the NMOS transistor.

- Additionally, the drain terminals of both NMOS and PMOS transistors are connected together, and the output is connected to this common drain node.

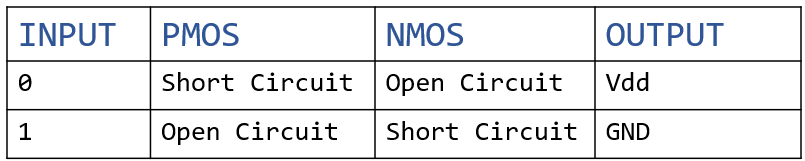

- For the PMOS transistor:

- When the input signal is 0, the source-to-drain terminal of the PMOS transistor acts as a closed or short circuit.

- When the input signal is 1, the source-to-drain terminal of the PMOS transistor acts as an open circuit. - For the NMOS transistor:

- When the input signal is 1, the source-to-drain terminal of the NMOS transistor acts as a closed or short circuit.

- When the input signal is 0, the source-to-drain terminal of the NMOS transistor acts as an open circuit. - This arrangement allows CMOS circuits to implement complementary logic functions efficiently, where one type of transistor conducts while the other is off, resulting in low power consumption and high noise immunity.

- Working:

- Input Signal = 0:

- When the input signal is 0, the PMOS (P-channel Metal-Oxide-Semiconductor) transistor in the CMOS circuit acts as a short circuit (conducting).

- At the same time, the NMOS (N-channel Metal-Oxide-Semiconductor) transistor acts as an open circuit (non-conducting).

As a result, the output is pulled up to the supply voltage (VDD), typically representing a logic high or 1. - Input Signal = 1:

- Conversely, when the input signal is 1, the PMOS transistor in the CMOS circuit acts as an open circuit (non-conducting).

- Meanwhile, the NMOS transistor acts as a short circuit (conducting).

Consequently, the output is pulled down to ground (GND), typically representing a logic low or 0.

- The below table summarizes the working of CMOS for ideal conditions.

- Under ideal conditions, a CMOS circuit acts as an inverter (NOT gate). This is because the complementary behavior of the PMOS and NMOS transistors in a CMOS inverter ensures that the output is the logical complement of the input signal.

- When the input is high (1), the output is low (0), and when the input is low (0), the output is high (1). This inversion behavior makes CMOS inverters fundamental building blocks in digital circuit design, allowing for logical operations and signal processing.

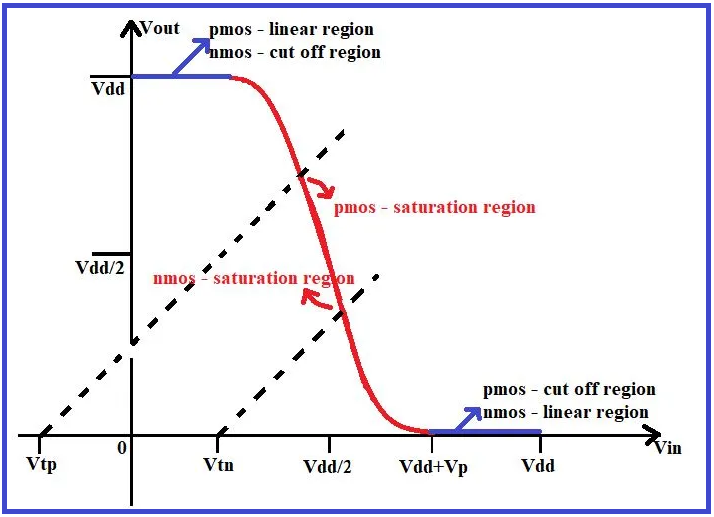

- Voltage transfer characteristics to CMOS inverter.

- Threshold Voltages:

- Vtn: Threshold voltage for NMOS transistor (positive value).

- ∣Vtp∣: Threshold voltage for PMOS transistor (absolute value, since it's negative). - Voltage Definitions:

- Vgsn: Voltage between the gate and source of NMOS.

- Vdsn: Voltage between the drain and source of NMOS.

- Vgsp: Voltage between the gate and source of PMOS.

- Vdsp: Voltage between the drain and source of PMOS. Vdd: Supply voltage. - Conditions for Operation:

NMOS Transistor:

- When Vgsn<Vtn, the NMOS transistor is in the cutoff region (off state).

- When Vgsn>Vtn:

If Vgsn−Vtn>Vdsn, the NMOS transistor is in the linear region.

If Vgsn−Vtn<Vdsn, the NMOS transistor is in the saturation region.

PMOS Transistor:

- When ∣Vgsp>∣Vtp∣, the PMOS transistor is in the cutoff region (off state).

- When ∣Vgsp<∣Vtp∣:

If Vgsp−∣Vtp∣<Vdsp, the PMOS transistor is in the linear region.

If Vgsp−∣Vtp∣>Vdsp, the PMOS transistor is in the saturation region.

4. Voltage Transfer Characteristics:

Input = 0 (Logic Low):

- NMOS Transistor: Vgsn<Vtn, NMOS is off (cutoff region).

- PMOS Transistor: ∣Vgsp>∣Vtp∣, PMOS is off (cutoff region).

- Output = Vdd (Logic High).

Input = 1 (Logic High):

- NMOS Transistor: Vgsn>Vtn, NMOS is on (linear/saturation region).

- PMOS Transistor: ∣Vgsp<∣Vtp∣, PMOS is on (linear/saturation region).

- Output = GND (Logic Low).

Below graph shows the Voltage Transfer characteristics of CMOS.

- Advantages of CMOS Technology:

CMOS technology offers numerous advantages, including low power consumption due to negligible static current, high noise margins, and scalability to smaller process nodes. These advantages have made CMOS the dominant technology in digital design.

- CMOS Process Technology:

The CMOS (Complementary Metal-Oxide-Semiconductor) fabrication process involves several key steps to create integrated circuits. It typically starts with a silicon wafer, which undergoes cleaning and oxidation to create a thin layer of silicon dioxide (SiO2) on its surface. Photolithography is then used to pattern the wafer with photoresist, allowing for the creation of transistor structures through processes like ion implantation and diffusion to create the n-type and p-type regions.

Next, thin layers of metal (often aluminum or copper) are deposited and patterned using techniques like sputtering and etching to create the metal interconnects that link transistors and other components. Dielectrics, such as silicon dioxide or silicon nitride, are deposited and etched to isolate and insulate different parts of the circuit.

Each step requires precision and control to ensure the desired electrical characteristics and performance of the CMOS integrated circuit.

- CMOS Scaling and Moore’s Law:

CMOS scaling refers to the continuous reduction in the size of CMOS (Complementary Metal-Oxide-Semiconductor) transistors and the overall components of integrated circuits. This scaling is a fundamental aspect of semiconductor technology advancement and is driven by the desire to increase the performance, density, and efficiency of electronic devices.

As transistors and other components are scaled down, their dimensions shrink, leading to several benefits such as higher integration density (more components in a smaller area), reduced power consumption, faster operation speeds, and lower manufacturing costs per unit. CMOS scaling has been a driving force behind the miniaturization of electronic devices and the development of increasingly complex integrated circuits.

Moore’s Law, formulated by Gordon Moore, states that the number of transistors on a microchip doubles approximately every two years, leading to a doubling of computing power and performance. This observation has been a guiding principle in the semiconductor industry and has driven continuous innovation and improvement in semiconductor technology.

- Applications of CMOS in VLSI Design:

CMOS technology finds extensive use in VLSI design, powering microprocessors, memory chips, ASICs, and FPGA devices. Its low power consumption and high integration density make it ideal for designing complex digital systems.

In conclusion, CMOS technology stands as a pivotal force in modern digital design, offering a multitude of advantages such as low power consumption, high noise immunity, and scalability. Its fundamental principles, including complementary transistor behavior and efficient logic functions, make it a preferred choice for a wide range of applications in VLSI design, from microprocessors to memory chips and beyond. The CMOS fabrication process, with its precise steps and control, enables the creation of highly integrated circuits with exceptional performance and efficiency. As CMOS scaling continues to drive technological advancement, in tandem with Moore’s Law, the future of semiconductor technology remains promising, paving the way for even more sophisticated and powerful electronic devices.

No comments:

Post a Comment