jk_flip_flop.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity jk_flip_flop is

Port ( J, K, CLK : in STD_LOGIC;

Q, Qb : out STD_LOGIC);

end jk_flip_flop;

architecture Behavioral of jk_flip_flop is

begin

process (J, K, CLK)

variable temp: std_logic;

begin

if (rising_edge(CLK)) then

if(J=’0' and K=’0')then

temp:=temp;

elsif(J=’0' and K=’1')then

temp:=’0';

elsif(J=’1' and K=’0')then

temp:=’1';

elsif(J=’1' and K=’1')then

temp:=not temp;

else null;

end if;

end if;

Q<=temp;

Qb<= not temp;

end process;

end Behavioral;

tb_jk_flip_flop.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tb_jk_flip_flop is

end entity;

architecture Behavioural of tb_jk_flip_flop is

component jk_flip_flop is

Port ( J, K, CLK: in STD_LOGIC;

Q, Qb : out STD_LOGIC);

end component ;

signal J, K, CLK, Q, Qb : STD_LOGIC;

begin

uut: jk_flip_flop port map(

J => J,

K => K,

CLK => CLK,

Q => Q,

Qb => Qb);

Clock : process

begin

CLK <= ‘1’;

wait for 10 ns;

CLK <= ‘0’;

wait for 10 ns;

end process;

stim : process

begin

J <= ‘0’ ; K<=’0';

wait for 20 ns;

J <= ‘0’ ; K<=’1';

wait for 20 ns;

J <= ‘1’ ; K<=’0';

wait for 20 ns;

J <= ‘1’ ; K<=’1';

wait for 20 ns;

end process;

end Behavioural;

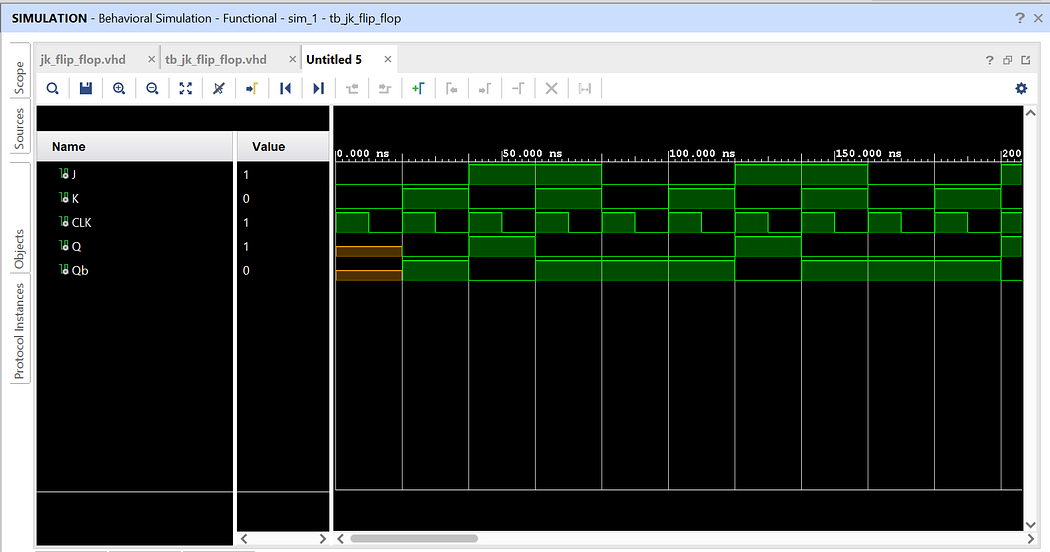

The output waveform for JK Flip Flop will be as follows:

No comments:

Post a Comment