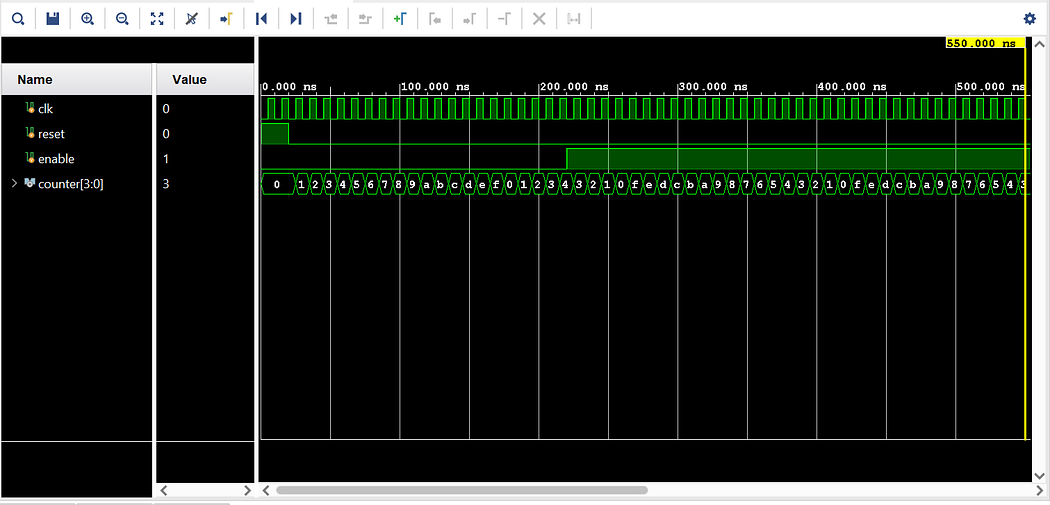

up_down_counter.v

module up_down_counter(clk, reset, enable, counter);

input clk, reset, enable;

output[3:0] counter;

reg[3:0] count;

always @(posedge clk or posedge reset)

begin

if(reset)

count<=4'h0;

else if (~enable)

count<=count+4'd1;

else

count<=count-4'd1;

end

assign counter = count;

endmodule

tb_up_down_counter.v

module tb_up_down_counter();

reg clk, reset,enable;

wire[3:0] counter;

up_down_counter uut(clk,reset,enable,counter);

initial begin

$display(“Testing UP DOWN Counter”);

clk=0;

forever #5 clk=~clk;

end

initial begin

reset=1;

enable=0;

#20;

reset=0;

#200;

enable=1;

end

endmodule

No comments:

Post a Comment