xnor_gate.v

module xnor_gate(a,b,y);

input a;

input b;

output y;

xnor(y,a,b);

endmodule

tb_xnor_gate.v

module tb_xnor_gate;

reg a;

reg b;

wire y;

xnor_gate UUT (.a(a), .b(b), .y(y));

initial begin

$display(“Testing XNOR gate”);

a = 0; b=0;

#10;

$display(“Input_A = %b, Input_B = %b, Output = %b”, a,b,y);

a = 0; b=1;

#10;

$display(“Input_A = %b, Input_B = %b, Output = %b”, a,b,y);

a = 1; b=0;

#10;

$display(“Input_A = %b, Input_B = %b, Output = %b”, a,b,y);

a = 1; b=1;

#10;

$display(“Input_A = %b, Input_B = %b, Output = %b”, a,b,y);

$finish;

end

endmodule

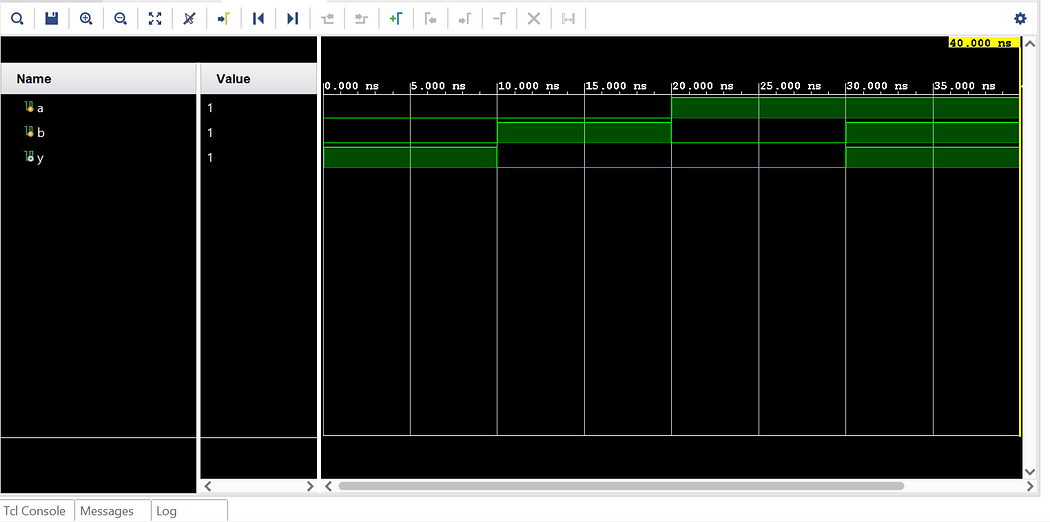

The output waveform for xnor gate will be as follows:

No comments:

Post a Comment